CMOS模擬集成電路版圖設(shè)計(jì)第五章 Calibre驗(yàn)證文件詳解與集成電路設(shè)計(jì)流程

集成電路設(shè)計(jì)是一個(gè)高度復(fù)雜且嚴(yán)謹(jǐn)?shù)倪^程,其中版圖設(shè)計(jì)完成后,必須通過一系列嚴(yán)格的物理驗(yàn)證才能確保芯片功能的正確性與制造的可靠性。Calibre作為業(yè)界領(lǐng)先的物理驗(yàn)證工具,其驗(yàn)證文件的編寫與執(zhí)行是連接設(shè)計(jì)與制造的關(guān)鍵橋梁。本章將深入探討Calibre驗(yàn)證文件的基礎(chǔ)、核心方法及其在集成電路設(shè)計(jì)流程中的關(guān)鍵作用。

一、Calibre驗(yàn)證文件基礎(chǔ):DRC、LVS與ERC

Calibre驗(yàn)證主要包含三大核心部分:設(shè)計(jì)規(guī)則檢查(DRC)、版圖與電路圖一致性檢查(LVS)和電氣規(guī)則檢查(ERC)。

- 設(shè)計(jì)規(guī)則檢查(DRC):這是物理驗(yàn)證的首要步驟。DRC文件(通常以

.calibre或.drv為擴(kuò)展名)由代工廠(Foundry)提供,其中定義了芯片制造工藝所必須遵守的所有幾何規(guī)則。例如,晶體管的最小溝道長度、金屬線的最小寬度和間距、接觸孔的大小及覆蓋范圍等。Calibre DRC工具會根據(jù)這些規(guī)則,自動檢查版圖中所有圖形層是否存在違反規(guī)則的情況,并生成詳細(xì)的錯(cuò)誤報(bào)告。確保DRC Clean是版圖流片(Tape-out)的基本前提。

- 版圖與電路圖一致性檢查(LVS):LVS驗(yàn)證旨在確保實(shí)際繪制的版圖(Layout)與電路設(shè)計(jì)原理圖(Schematic)在電氣連接上完全一致。LVS驗(yàn)證文件(通常包含

.calibre、.lvs等文件)會提取版圖中的器件(如MOS管、電阻、電容)和連接關(guān)系(Netlist),并與原理圖網(wǎng)表進(jìn)行比對。LVS驗(yàn)證不僅檢查器件類型、數(shù)量是否匹配,更重要的是驗(yàn)證所有節(jié)點(diǎn)的連接關(guān)系是否正確。LVS通過是保證芯片功能正確的關(guān)鍵。

- 電氣規(guī)則檢查(ERC):ERC主要檢查版圖中潛在的電氣問題,這些問題可能不違反幾何設(shè)計(jì)規(guī)則,但會導(dǎo)致電路失效。例如,檢查是否存在浮空的柵極(Gate)、電源和地之間是否短路、襯底連接是否正確等。ERC規(guī)則通常也包含在LVS或獨(dú)立的規(guī)則文件中,是DRC和LVS的重要補(bǔ)充。

二、Calibre驗(yàn)證文件的核心方法與編寫要點(diǎn)

- 規(guī)則文件結(jié)構(gòu):典型的Calibre規(guī)則文件采用層次化的語法結(jié)構(gòu)。它通常包括頭文件聲明、層定義、規(guī)則主體等部分。層定義將版圖數(shù)據(jù)(GDS/OASIS文件中的層號)映射到Calibre內(nèi)部用于運(yùn)算的邏輯層。規(guī)則主體則使用豐富的命令和運(yùn)算符(如AND、OR、NOT、SIZE、ENCLOSE等)來描述復(fù)雜的幾何與電氣約束。

- 層操作與衍生層:驗(yàn)證的核心是對圖形層進(jìn)行邏輯運(yùn)算,生成“衍生層”。例如,要檢查金屬1(M1)與多晶硅(Poly)的最小間距,需要先定義M1層和Poly層,然后使用

SPACE命令對兩者進(jìn)行間距檢查。通過組合不同的層操作,可以構(gòu)建出非常復(fù)雜的檢查場景,如檢查天線效應(yīng)(Antenna Rule)、阱間距(Well Proximity)等。

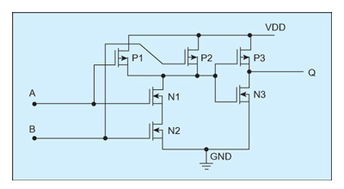

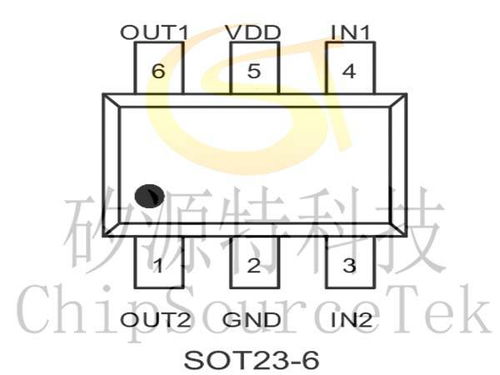

- 器件識別與屬性提取:在LVS文件中,最關(guān)鍵的部分是“器件識別”模塊。它通過一系列層操作,從版圖中“切割”并識別出一個(gè)個(gè)獨(dú)立的器件。例如,一個(gè)NMOS管可以通過有源區(qū)(Active)、多晶硅(Poly)以及N型注入層(N_imp)的交疊來定義。識別后,還需要提取器件的屬性,如MOS管的寬(W)和長(L)。這些信息將與原理圖網(wǎng)表中的器件參數(shù)進(jìn)行比對。

- 連接關(guān)系提取:LVS的另一核心是提取連接關(guān)系。通過定義連接層(如金屬層、接觸孔/通孔層),Calibre可以自動生成版圖的電氣連接網(wǎng)表。驗(yàn)證文件需要明確定義哪些層之間通過接觸孔相連,從而構(gòu)建出完整的導(dǎo)電通路。

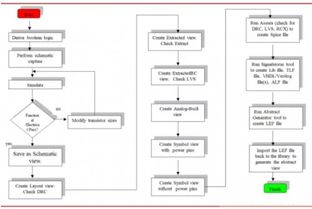

三、驗(yàn)證流程與集成電路設(shè)計(jì)整合

在完整的集成電路設(shè)計(jì)流程中,Calibre驗(yàn)證并非一次性工作,而是與版圖設(shè)計(jì)迭代并行的過程。

- 交互式驗(yàn)證(Online Verification):現(xiàn)代版圖設(shè)計(jì)工具(如Cadence Virtuoso)通常與Calibre深度集成,支持在繪制版圖的同時(shí)實(shí)時(shí)或快速進(jìn)行DRC和LVS檢查。這允許設(shè)計(jì)者及時(shí)發(fā)現(xiàn)并修正錯(cuò)誤,極大提高了設(shè)計(jì)效率。

- 簽核驗(yàn)證(Sign-off Verification):在版圖最終完成后,需要進(jìn)行全面、嚴(yán)格的“簽核”驗(yàn)證。這通常是離線的、批處理式的完整運(yùn)行,確保在所有工藝角(Corner)下,DRC、LVS和ERC都完全通過。只有簽核驗(yàn)證通過,版圖數(shù)據(jù)才能交付給代工廠進(jìn)行掩模制作。

- 與寄生參數(shù)提取的協(xié)同:物理驗(yàn)證通過后,通常還需要使用Calibre xRC等工具從驗(yàn)證后的潔凈版圖中提取寄生電阻和電容(PEX),生成帶寄生參數(shù)的電路網(wǎng)表。將此網(wǎng)表反標(biāo)(Back-annotate)到電路仿真器中,進(jìn)行后仿真(Post-layout Simulation),以驗(yàn)證版圖寄生效應(yīng)是否影響電路性能(如速度、功耗、噪聲等)。這是確保設(shè)計(jì)成功的關(guān)鍵一步。

四、

Calibre驗(yàn)證文件是連接CMOS模擬集成電路設(shè)計(jì)與制造的“法律文書”和“質(zhì)量檢測標(biāo)準(zhǔn)”。掌握其基礎(chǔ)語法、理解DRC、LVS、ERC的核心原理與方法,并熟練將其融入迭代設(shè)計(jì)流程,是每一位模擬版圖工程師和芯片設(shè)計(jì)者的必備技能。一個(gè)潔凈、驗(yàn)證通過的版圖,是芯片從設(shè)計(jì)藍(lán)圖變?yōu)槲锢韺?shí)體的堅(jiān)實(shí)保障。通過嚴(yán)謹(jǐn)?shù)奈锢眚?yàn)證,才能最大程度地降低流片風(fēng)險(xiǎn),提高芯片的一次成功率。

如若轉(zhuǎn)載,請注明出處:http://www.ruilinz.cn/product/64.html

更新時(shí)間:2026-02-04 06:04:28